לוח ההערכה שקיבלתי במתנה מ-Microchip מהווה הזדמנות מצוינת להסביר ולהדגים את ה-CLC – אחד מהמודולים הפריפריאליים המוזרים והמעניינים ביותר שצצים במיקרו-בקרים בשנים האחרונות.

חומרה ייעודית תהיה לעולם מהירה יותר מתוכנה, וכאשר חומרה של מיקרו-בקר מסוגלת לבצע מטלה כלשהי ללא פיקוח רצוף של תוכנה, הדבר יכול להיות שווה ערך למגהרצים שלמים של מהירות שעון, לעשרות או מאות בייטים של זיכרון, וגם לשעות סוללה. לכן – ובמיוחד בעולם ה-8 וה-16 ביט, שמתקשה להתמודד עם כוח העיבוד הגולמי של מעבדי ה-32 ביט – אנחנו רואים עוד ועוד המצאות וחידושים בתחום של המודולים הפריפריאליים: החל מיכולות וותיקות ו"מובנות מאליהן" כמו הפקת PWM רק ברזולוציה גבוהה יותר, ועד להצפנות מתקדמות או חישובי CRC לווידוא תקינות מידע.

לפני שנה, בערך, הצגתי מודול פריפריאלי מסקרן של מיקרו-בקרים מסוימים ממשפחת PIC: ה-Data Signal Modulator. מודול זה איפשר לי להרכיב אות שידור (TX) של UART על גבי אות PWM בתדר 38KHz, וכך לשדר מידע באינפרה-אדום כמעט באפס מאמץ מבחינת המעבד. מתחת למכסה המנוע, ה-DSM מבצע למעשה פעולת AND לוגית על ערכי 0 ו-1 שמגיעים משניים או שלושה מקורות שונים.

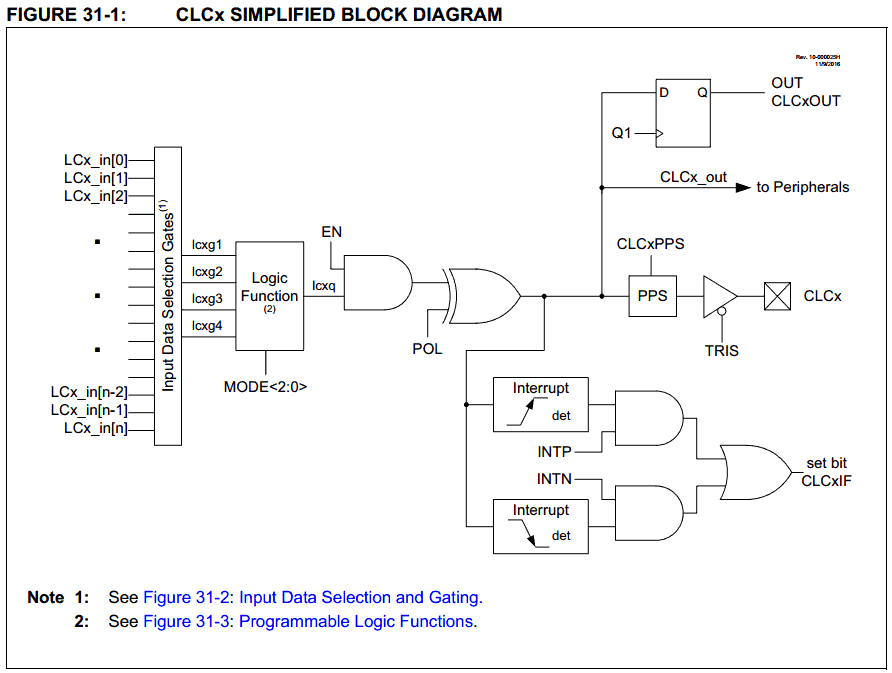

מודול ה-CLC, ראשי תיבות של Configurable Logic Cell, הוא בעצם הרחבה והכללה של אותו עיקרון. הוא מאפשר לנו לבחור עד ארבעה מקורות שונים לערכי 0 ו-1 (המקורות האלה יכולים להיות פיני קלט, שעוני מערכת, טיימרים או מודולים אחרים), ולבצע עליהם אחת מתוך מבחר פעולות לוגיות, כשכל זה מתרחש בלי התערבות של המעבד. המשמעות היא שהפעולות הלוגיות האלה יכולות להתבצע בקצב מהיר הרבה יותר מקצב השעון של המערכת, ואפילו כשהמיקרו-בקר נמצא במצב שינה חסכוני בחשמל!

העבודה עם CLC דומה לעבודה עם ג'וקים פשוטים של שערים לוגיים ודלגלגים (Flip Flops), כמו שלומדים בשיעורים וקורסי מבוא למערכות ספרתיות. זו צורת חשיבה שונה מהשיטה האלגוריתמית של כתיבת תוכנה, ומי שהגיע מעולם הארדואינו יצטרך להשלים חומר ולאמץ פרספקטיבה קצת שונה כדי לתפוס מה הולך פה.

כדי להדגים את השימוש ב-CLC בחרתי ליצור מערכת בסיסית מאוד, עם שלושה לחצנים, שנמצאת רוב הזמן במצב שינה. כדי להעיר אותה, המשתמש חייב ללחוץ על שלושת הלחצנים בו זמנית. איך היינו מבצעים דבר כזה ללא CLC? אילו היינו מסתמכים על פסיקות חיצוניות בלבד, כל לחצן היה מעיר את המיקרו-בקר, ואז היינו צריכים לבדוק בתוכנה אם גם שאר הלחצנים לחוצים, ואם לא אז לחזור לישון. זה בזבזני, וגם מסרבל את הקוד אם אנחנו צריכים בנוסף את הפסיקות האלה בשביל הפונקציונליות הרגילה של הלחצנים. אפשרות אחרת היא להציב ג'וק חיצוני שישמש כשער AND לשלושת הסיגנלים, אבל גם הוא יצרוך חשמל ויתפוס מקום.

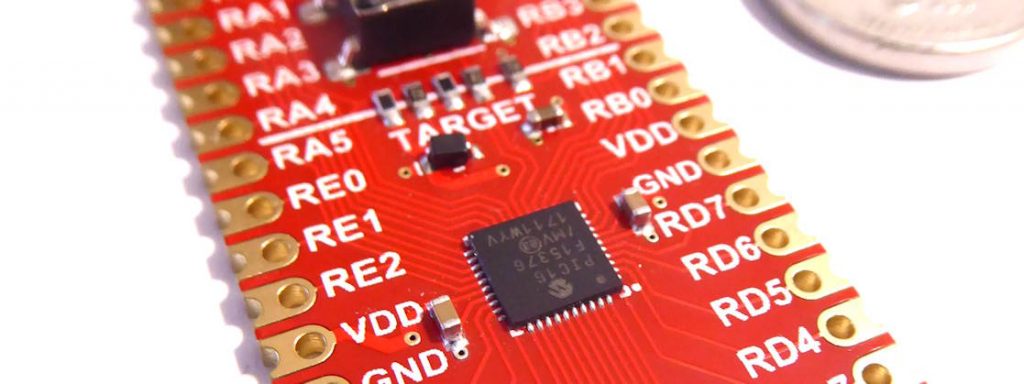

את התוכנית כתבתי ללוח ההערכה המינימליסטי שקיבלתי כאמור מ-Microchip, אחרי שהשתתפתי בצ'אט פומבי עם נציגי החברה ב-hackaday.io. המיקרו-בקר הראשי שעל הלוח הוא PIC16F15376, שכולל ארבעה מודולי CLC נפרדים. בדומה ללוח שהצגתי כאן, גם הנוכחי מיועד רשמית לעבודה עם סביבת הפיתוח המקוונת MPLAB Xpress, אבל אין שום בעיה להעלות אליו קוד שהופק ב-MPLAB X הרגילה. בינתיים לא מצאתי מידע רשמי על הלוח הזה, ונראה שהוא לא מוצע למכירה*.

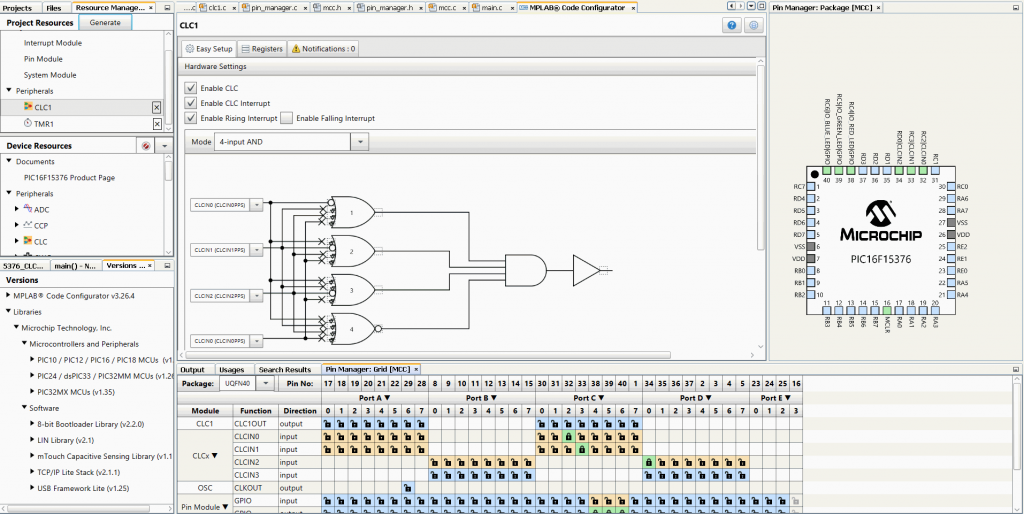

את ה-CLC, כמו את כל המודולים האחרים, מתכנתים בסופו של דבר באמצעות קביעת ביטים בכל מיני רגיסטרים, אבל הפעם – כדי לחסוך זמן – בחרתי להיעזר ב-MCC, הכלי הגרפי לניהול הגדרות שמשולב בסביבת הפיתוח. זה לא המקום להיכנס לפרטי העבודה איתו; הנה צילום מסך של הטופס שבו הגדרתי את ה-CLC:

הציור באמצע אמור להיות מוכר למי שלמד אפילו קצת שערים לוגיים. שלושת הסיגנלים (משמאל, התחתון לא בשימוש) מגיעים מפיני GPIO, ואני מבצע עליהם קודם כל פעולת NOT לוגית כי הפינים מחוברים ללחצנים שמקצרים אותם לאדמה, והוגדר להם weak pull up פנימי. הסיגנלים מתנקזים לשער AND יחיד, ורק אם כולם 1 אז גם הפלט של ה-CLC (מימין) יהיה 1. הפעלתי פסיקה על עלייה של הפלט הזה מ-0 ל-1, וכך לחיצה על שלושת הלחצנים יכולה להעיר את המיקרו-בקר משנתו. אגב, את הפלט של ה-CLC אפשר לנתב הלאה לפין GPIO או למודולים אחרים, וגם לקרוא אותו בתוכנה.

הטריק עובד יפה. בהתחשב בדרישות, זו ללא ספק הדרך הכי קלה לממש את עניין ההתעוררות של המערכת – אבל כמובן שיש לה מחיר מסוים: ה-CLC עצמו צורך קצת חשמל (ולהוכחה, הוא אחד מהמודולים שאפשר לנטרל בעזרת הרגיסטרים הייעודיים לחיסכון בחשמל). לרוע המזל, לא הצלחתי למצוא בשום מקום מידע על הזרם שמודול ה-CLC צורך בפועל, וגם אין לי דרך למדוד את הצריכה עם הלוח הספציפי הזה, שפועלים בו רכיבים נוספים. העניין הזה יצטרך לחכות למיקרו-בקר ולמעגל אחרים.

הרעיון של שערים לוגיים ניתנים-לתכנות הוא ממש לא חדש. למשל, יש עולם שלם של FPGA, ג'וקים עמוסים חומרה ניתנת-לתכנות שמשתמשים בהם לרוב למשימות שדורשות עיבודים מאוד ספציפיים במהירות גבוהה. גם ב-PSoC של Cypress, המודולים הפריפריאליים ממומשים למעשה על גבי מערכים גדולים של שערים לוגיים, והמשתמש המתקדם מוזמן לעצב מודולים משלו. אבל במיקרו-בקרים "קלאסיים" זהו קונספט חדש יחסית. במובן מסוים הוא מהווה צעד לאחור, בזה שהוא מכריח את המתכנת לחזור למושגים ולטכניקות בסיסיים יותר. מצד שני, יש ל-CLC כאמור יכולות ייחודיות וגמישות רבה, וכל יחידה כזו עשויה לפתור בעיות תכנון (נפוצות או מיוחדות במינן) במינימום השקעה לעומת פתרונות חלופיים.

הנה מסמך "טיפים וטריקים" של Microchip לשימוש ב-CLC. חשוב לציין שבמיקרו-בקרים של חברות שונות, המודולים האלה ממומשים ומתוכנתים בצורות אחרות, וגם נקראים בשמות שונים. כרגיל, אין תחליף לקריאה של ה-Datasheet.

*תוספת מאוחרת: מאז שכתבתי את הפוסט הזה, הלוח הופיע באתר של Microchip. המיקרו-בקר שמוזכר שם שונה מזה שאצלי, לא ברור אם זו שגיאה או שינוי מכוון. הלוח עולה 12 דולר, לא כולל משלוח.

דרך למדידת זרם:

יש למדוד צריכת זרם ב deep idle (או איך שקוראים למצב שינה עמוקה ב pic). כמובן לוודא שכל הפינים שמקונפגים כ input לא נדחפים (כלומר לא צפים). מודדיםמפעם אחת כש ה clc מאופשר ופעם כשהוא כבוי.

מכיוון שלפי הסכימה מדובר במספר שערים קטן, מאמין שה delta תהיה כמה nAmp

נכון, ואין לי כלי מדידה שיכול לתת רזולוציה של nA כששאר הרכיבים על הלוח לוקחים כמה mA…

אז בעצם שמו logic cell אחד של fpga בפנים? קונספט מעניין.

מה עם FPGA באמת עידו? יש לך אי אלו כוונות לנסות להתעסק בזה? D:

לא אחד, ארבעה.

ולגבי FPGA, לא, כרגע זה Low-level מדי אפילו בשבילי 🙂

FPGA מתוכנת בVHDL וכדומה. לא שונה בהרבה מתכנות בסיסי.

הרבה אנשים יחלקו על ההצהרה הזאת 🙂

שונה מאד מתכנות בסיסי בגלל הרצף, תוכנה שנכתבת ב-VHDL או ב-Verilog מכילה הרבה יותר חלקים שרצים במקביל (משום שהם מייצגים חלקי חומרה נפרדים) לעומת תכנות שבו הכל סדרתי וכל פקודה מתבצעת רק אחרי הפקודה שלפניה.

זה מפיל המון מתכנתים בניסיונות הראשונים שלהם בשפות חומרה (HDL)